#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

#### Thesis for the Degree of Doctor

KoHPCG – High-Performance Conjugate Gradient Benchmark Program on Kokkos Performance Portability Framework

## KoHPCG - 이기종 환경에서 성능 이식성을 보장하는 Kokkos 프레임워크 기반의 HPCG 벤치마크 프로그램

**June 2025**

**Department of Computer Science and Engineering**

Graduate School of Soongsil University

MUHAMMAD RIZWAN

#### Thesis for the Degree of Doctor

## KoHPCG – High-Performance Conjugate Gradient Benchmark Program on Kokkos Performance Portability Framework

KoHPCG - 이기종 환경에서 성능 이식성을 보장하는 Kokkos 프레임워크 기반의 HPCG 벤치마크 프로그램

**June 2025**

**Department of Computer Science and Engineering**

**Graduate School of Soongsil University**

**MUHAMMAD RIZWAN**

#### Thesis for the Degree of Doctor

## KoHPCG – High-Performance Conjugate Gradient Benchmark Program on Kokkos Performance Portability Framework

Thesis Supervisor: Prof. Dr. Jaeyoung Choi

# Thesis submitted in partial fulfillment of the requirements for the Degree of Doctor

**June 2025**

**Department of Computer Science and Engineering**

**Graduate School of Soongsil University**

**MUHAMMAD RIZWAN**

# To approve the submitted thesis for the Degree of Doctor by MUHAMMAD RIZWAN

#### **Thesis Committee**

Member

Jongsun Choz (signature)

Member Myungho Lee (signature)

Member Imbunm (signature)

Member Jacyoung Choi Joignature)

June 2025

Department of Computer Science and Engineering

**Graduate School of Soongsil University**

#### **ACKNOWLEDGEMENT**

First and foremost, all praise is due to **Almighty Allah**, the Most Merciful and the Most Compassionate, who granted me the strength, patience, and perseverance to complete this endeavor. Without His divine guidance and mercy, this milestone would not have been possible.

This dissertation stands as a testament not only to individual effort, but to the unwavering support and inspiration of many remarkable individuals around me. I am deeply grateful to **my supervisor**, **Dr. Jaeyoung Choi**, for his invaluable guidance, insightful feedback, and continuous encouragement throughout my PhD journey. His mentorship, marked by both professionalism and kindness, has been a cornerstone of my academic growth.

I would like to express my heartfelt thanks to **my committee members** for their constructive suggestions and support. My appreciation also goes to all **lab mates** and alumni, whose contributions created a stimulating and collaborative research environment.

Special thanks go to **all my teachers** who laid the foundation for my academic journey. I am equally grateful to all individuals—named or unnamed—who supported me directly or indirectly with their encouragement, assistance, and prayers.

I extend my sincerest gratitude to my parents and family members, whose love,

patience, and unwavering belief in me have been the cornerstone of my motivation.

I also want to acknowledge the friendship and solidarity of my fellow countrymen

as well as **friends from around the world**, who brought joy and perspective into this

journey with their diverse experiences.

Finally, to all those who helped me along the way, even if your name is not listed

here, please accept my deepest thanks. Your support was valuable and will always be

remembered.

Date: June 2025

**MUHAMMAD RIZWAN**

## **TABLE OF CONTENTS**

| ABSTRACT IN ENGLISH                                                                                                                             | xi                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| ABSTRACT IN KOREAN                                                                                                                              | xiii               |

| CHAPTER 1. Introduction                                                                                                                         | 1                  |

| 1.1 Motivation                                                                                                                                  | 3                  |

| 1.2 Problem Statement                                                                                                                           | 4                  |

| 1.3 Research Objectives and Contributions                                                                                                       | 5                  |

|                                                                                                                                                 | 6                  |

| 1.4 Thesis Organization                                                                                                                         | U                  |

| 1.4 Thesis Organization                                                                                                                         | 8                  |

|                                                                                                                                                 |                    |

| CHAPTER 2. Background                                                                                                                           | 8                  |

| CHAPTER 2. Background  2.1 HPCG                                                                                                                 | <b>8</b>           |

| CHAPTER 2. Background  2.1 HPCG                                                                                                                 | <b>8</b> 8         |

| CHAPTER 2. Background  2.1 HPCG  2.1.1 Preconditioned Conjugate Gradient Method  2.1.2 HPCG Execution Flow Process                              | 8<br>8<br>8        |

| CHAPTER 2. Background  2.1 HPCG  2.1.1 Preconditioned Conjugate Gradient Method  2.1.2 HPCG Execution Flow Process  2.1.3 Problem Setup in HPCG | 8<br>8<br>10<br>12 |

| 2.2 Kokkos EcoSystem                         | 22 |

|----------------------------------------------|----|

| 2.2.1 Programming Model                      | 23 |

| 2.2.2 Packages/Repositories                  | 25 |

| CHAPTER 3. Literature Review                 | 27 |

| 3.1 HPCG Optimization Techniques             | 27 |

| 3.1.1 CPU-Based Systems                      | 28 |

| 3.1.2 GPU-Based Systems                      | 36 |

| 3.1.3 Hybrid Architectures                   | 37 |

| 3.1.4 Other Architectures and Environments   | 39 |

| 3.1.5 HPCG Benchmark Implementation Variants | 41 |

| 3.1.6 Summary                                | 43 |

| 3.1.7 Supplementary Influential Works        | 44 |

| CHAPTER 4. Technique and Trends in HPCG      | 46 |

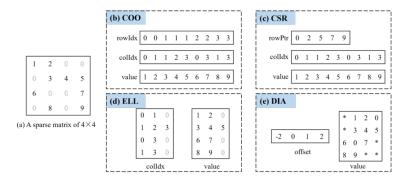

| 4.1 Data Formats and Storage Strategies      | 46 |

| 4.1.1 Common Sparse Matrix Formats           | 46 |

| 4.1.2 Novel Data Structures for HPCG         | 48 |

| 4.2 Parallelization Optimization Techniques  | 50 |

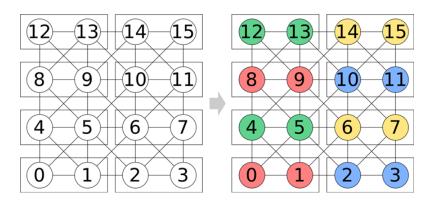

| 4.2.1 Coloring                               | 50 |

| 4.2.2 Multi Level Task Dependency Graph      | 55 |

| 4.2.3 Hyperplane                             | 56 |

| 4.2.4 Hierarchical Grid (HG)                        | 56 |

|-----------------------------------------------------|----|

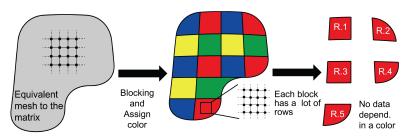

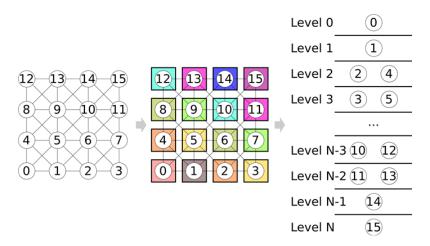

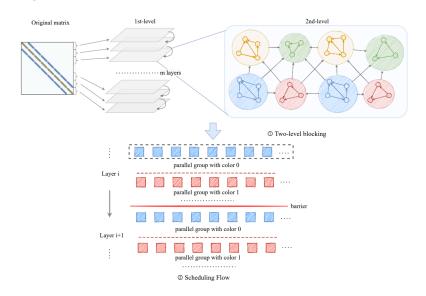

| 4.2.5 Two-level Blocking Scheme                     | 57 |

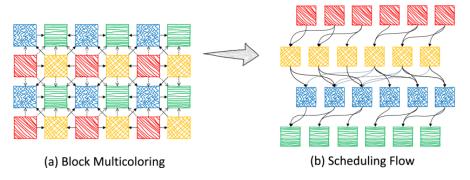

| 4.2.6 Block Multi-Color Scheduling (BMC) Scheduling | 58 |

| CHAPTER 5. Parallel Implementation of Symmetric     |    |

| Gauss-Seidel (SymGS) Variants                       | 61 |

| 5.1 Reference SymGS and its parallel variants       | 61 |

| 5.2 Our Designed Variants                           | 63 |

| 5.2.1 Temporal Block SymGS                          | 63 |

| 5.2.2 Over Relaxation SymGS                         | 63 |

| 5.2.3 Wavefront SymGS                               | 67 |

| 5.3 Experiments and Results                         | 68 |

| 5.3.1 Methodology                                   | 68 |

| 5.3.2 Settings                                      | 69 |

| 5.3.3 Performance metrics                           | 70 |

| 5.3.4 Results on Knights Landing (KNL)              | 72 |

| 5.3.5 Results on Skylake (SKL)                      | 81 |

| 5.4 Observations and Discussion                     | 86 |

| 5.4.1 Parallelism                                   | 87 |

## CHAPTER 6. KoHPCG – High-Performance

| Conjugate Gradient Benchmark Program on Kokkos    |     |

|---------------------------------------------------|-----|

| Performance Portability Framework                 | 90  |

| 6.1 Kokkos-Based Implementation                   | 91  |

| 6.2 Experiments and Results                       | 94  |

| 6.2.1 Experimental Setup                          | 94  |

| 6.2.2 Results on Knights Landing (KNL)            | 95  |

| 6.2.3 Results on Skylake Scalable Processor (SKL) | 98  |

| 6.2.4 Results on GPU Based System                 | 100 |

| CHAPTER 7. Conclusion                             | 101 |

| 7.1 Future Research Directions                    | 102 |

| REFERENCES                                        | 103 |

## LIST OF TABLES

| 3.1 | HPCG benchmark variants and implementation references        | 42 |

|-----|--------------------------------------------------------------|----|

| 4.1 | Common sparse matrix data formats                            | 47 |

| 4.2 | Data formats reported in literature of the HPCG optimization | 49 |

| 5.1 | Performance comparison of SymGS variants on KNL              | 74 |

| 5.2 | Performance comparison of SymGS variants on SKL              | 82 |

## LIST OF FIGURES

| 2.1 | HPCG execution process flow                               | 11 |

|-----|-----------------------------------------------------------|----|

| 2.2 | 27 point stencil in HPCG                                  | 12 |

| 2.3 | Geometric multigrid V-cycle in HPCG                       | 22 |

| 2.4 | Kokkos ecosystem overview                                 | 23 |

| 4.1 | Data formats illustration                                 | 46 |

| 4.2 | Multi-coloring                                            | 51 |

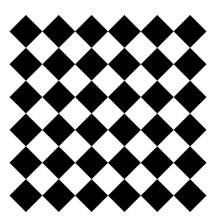

| 4.3 | Red-Black coloring                                        | 52 |

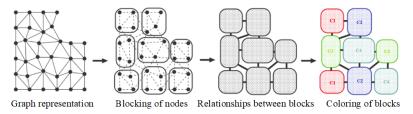

| 4.4 | Block multi-coloring                                      | 53 |

| 4.5 | Algebraic block multi-coloring                            | 54 |

| 4.6 | Multi-level task dependency graph                         | 55 |

| 4.7 | Hyperplane (2D)                                           | 56 |

| 4.8 | A two-level blocking scheme                               | 58 |

| 4.9 | Block multi-coloring with synchronization sparsification  | 60 |

| 5.1 | Execution flow of SymGS variants and HPCG                 | 69 |

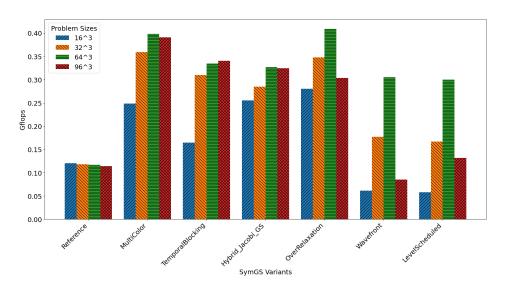

| 5.2 | Performance comparison of SymGS variants on 1 MPI process | 75 |

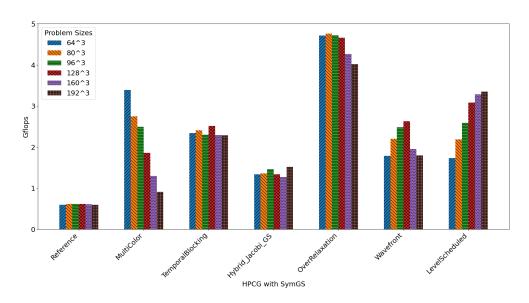

| 5.3 | Performance of HPCG using different SymGS variants on KNL        | 76 |

|-----|------------------------------------------------------------------|----|

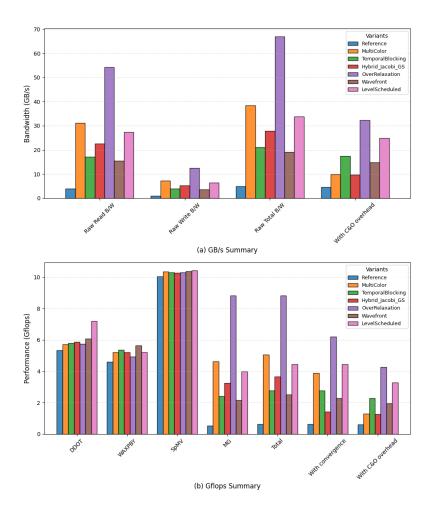

| 5.4 | Performance and Bandwidth Summary of HPCG                        | 78 |

| 5.5 | Performance comparison of (a) MG (Multigrid) and (b) HPCG on KNL | 80 |

| 5.6 | SymGS variants and their impact in HPCG on SKL                   | 82 |

| 5.7 | Performance of MG and HPCG on multi-node SKL                     | 84 |

| 6.1 | Performance comparison of HPCG variants on KNL                   | 96 |

| 6.2 | KoHPCG vs. Reference HPCG on multi-node Intel KNL                | 97 |

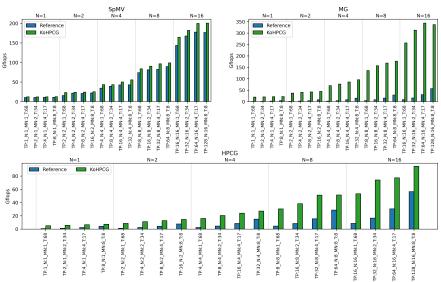

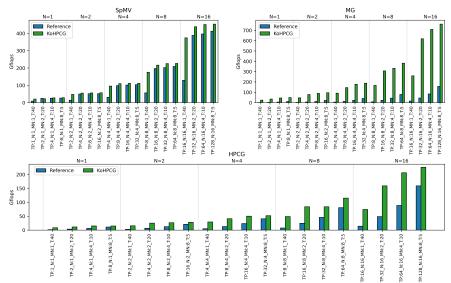

| 6 3 | Performance for SpMV MG and HPCG on Intel SKL                    | 98 |

## **GLOSSARY**

| ABMC     | Algebraic Block Multi-Coloring             |

|----------|--------------------------------------------|

| ADB      | Assignable Data Buffer                     |

| ALP      | ALP/GraphBLAS programming framework        |

| AMD      | Advanced Micro Devices                     |

| AVL      | Architectural Vector Length                |

| BMC      | Block Multi-Coloring                       |

| BFS      | Breadth-First Search                       |

| CG       | Conjugate Gradient                         |

| COO      | Coordinate                                 |

| CSC      | Compressed Sparse Column                   |

| CSCS     | Swiss National Supercomputing Centre       |

| CPE      | Core Processing Elements                   |

| CPU      | Central Processing Unit                    |

| CSR      | Compressed Sparse Row                      |

| CU       | Compute Unit                               |

| CUDA     | Compute Unified Device Architecture        |

| cuSPARSE | CUDA Sparse Matrix library                 |

| DDOT     | Double-precision DOT product               |

| DDR      | Double Data Rate (synchronous DRAM memory) |

| DIA      | Diagonal format                            |

| DOACROSS | A type of loop optimization technique      |

| DSCR     | Data Stream Control Register               |

| ELL      | ELLPACK                                    |

| FPGA     | Field-Programmable Gate Array              |

|          |                                            |

| GPU    | Graphics Processing Unit                     |

|--------|----------------------------------------------|

| GS     | Gauss-Seidel                                 |

| HBM    | High Bandwidth memory                        |

| HG     | Hierarchical Grid                            |

| HIP    | Heterogeneous-Compute Interface Library for  |

|        | Portability                                  |

| HPC    | High-Performance Computing                   |

| HPL    | High-Performance Linpack                     |

| HPCG   | High-Performance Conjugate Gradient          |

| HPGMG  | High Performance Geometric Multigrid         |

| IA     | Intel Architecture                           |

| IBM    | International Business Machines              |

| JAD    | Jagged Diagonal format Machines              |

| KHPCG  | Kokkos based HPCG Benchmark                  |

| KNL    | Xeon Phi Intel Knights Landing               |

| KOKKOS | A performance portable programming library   |

| LDM    | Local Device Memory                          |

| LS     | Level Scheduling                             |

| MC     | Multi-Coloring                               |

| MIC    | Many Integrated Core                         |

| MGM    | Multigrid Method                             |

| MGPCG  | Multi-Grid Preconditioned Conjugate Gradient |

| MKL    | Math Kernel Liberary                         |

| MPE    | Management Processing Elements               |

| MPI    | Message Passing Interface                    |

| NDP    | Near-Data Processors                         |

|        | NEC Vector Engine, A high-performance vector |

| NEC VE | processor architecture developed by NEC      |

|        | Corporation                                  |

| NVIDIA | A GPU manufacturer and designer company      |

| NUMA   | Non-uniform memory access                    |

| OpenMP | Open Multi-Processing                        |

|        |                                              |

| ORNL     | Oak Ridge National Laboratory                |

|----------|----------------------------------------------|

| PCG      | Preconditioned Conjugate Gradient            |

| PDE      | Partial Differential Equation                |

| PE       | Processing Element                           |

| RB       | Red-Black Coloring                           |

| RBGS     | Red-Black Gauss-Seidel                       |

| DIGG V   | Reduced Instruction Set Computing – V (fifth |

| RISC-V   | open-ISA generation)                         |

| Rmax     | Maximum Measured Performance                 |

| ROCm     | Radeon Open Compute                          |

| Rpeak    | Peak Performance                             |

| SELLPACK | A slieced variant of ELLPACK data format     |

| SIMD     | Single Instruction Multiple Data             |

| SpMV     | Sparse Matrix-Vector Multiplication          |

| SVE      | Scalable Vector Extension                    |

| SymGS    | Symmetric Gauss-Seidel                       |

| SX-ACE   | A vector parallel processor                  |

| SYCL     | Standard C++ for Heterogeneous Computing     |

| SKL      | Intel Skylake processors                     |

| TOP500   | A project ranks most powerful supercomputers |

| UMBC     | University of Maryland, Baltimore County     |

| VE       | Vector Engine                                |

| VPU      | Vector Processing Unit                       |

| WAXPBY   | Weighted A times X plus B times Y vector     |

| WAAPDI   | operation.                                   |

| Xilinx   | Xilinx is the company name (now owned by     |

| AIIIIX   | AMD), pioneer in FPGA technology             |

#### **ABSTRACT**

## KoHPCG – High-Performance Conjugate Gradient Benchmark Program on Kokkos Performance Portability Framework

#### **MUHAMMAD RIZWAN**

Department of Computer Science and Engineering

Graduate School of Soongsil University

The High-Performance Conjugate Gradient (HPCG) benchmark complements the HPL benchmark for supercomputing system evaluation. HPL emphasizes dense linear algebra operations with high floating-point performance, while HPCG emphasizes memory access patterns and sparse linear algebra operations that are common of many scientific applications to better assess modern supercomputing architectures. The memory-bound kernels of the reference HPCG implementation, especially the sequential Symmetric Gauss-Seidel (SymGS) routine and the bandwidth-limited Sparse Matrix-Vector Multiplication (SpMV) operation, limits performance.

This thesis introduces **KoHPCG**, a performance-portable HPCG benchmark using Kokkos programming model to address portability issues. The work begins with a thorough survey of HPCG optimizations to identify bottlenecks and improvements. Multiple algorithmic variants of the Symmetric Gauss-Seidel method are developed

and evaluated to improve parallel scalability without affecting the numerical accuracy.

The implementation translates all core HPCG kernels into Kokkos, including DDOT, WAXPBY, SpMV, SymGS, and MG operations. This uses Kokkos::Views for memory management, parallel execution, and execution and memory space abstractions to achieve performance portability across architectures. In multi-node configurations scaling up to 16 nodes, evaluated on Intel Xeon Phi (KNL) and Xeon Skylake (SKL) with MPI+OpenMP configurations. The results show significant improvements over the reference HPCG implementation and previous Kokkos-based variants like KHPCG.

The contributions of this work include: (1) a thorough analysis of HPCG optimization techniques and bottlenecks, (2) novel algorithmic variants of SymGS that improve parallel scalability, (3) a complete performance-portable implementation of HPCG using Kokkos, and (4) comprehensive performance evaluation on intel architectures. This research gives the HPC community a robust and extensible benchmarking framework for realistic performance evaluation on different systems, laying the groundwork for performance-portable HPCG improvements.

**Keywords:** High-Performance Conjugate Gradient (HPCG), Symmetric Gauss—Seidel (SymGS), Iterative Methods, Parallel Computing, Performance Optimization, Performance Portability, Kokkos, Multigrid (MG), High-Performance Computing (HPC).

국문초록

# KoHPCG - 이기종 환경에서 성능 이식성을 보장하는 Kokkos 프레임워크 기반의 HPCG 벤치마크 프로그램

리즈완 무하마드

컴퓨터학과

숭실대학교 대학원

HPCG (High-Performance Conjugate Gradient) 벤치마크는 슈퍼컴퓨팅 시스템 평가를 위한 HPL 벤치마크를 보완합니다. HPL은 높은 부동소수점 연산 성능을 갖춘 조밀한 선형대수 연산을 강조하는 반면, HPCG는 과학적 응용에서 흔히 나타나는 메모리 접근 패턴 및 희소 선형대수 연산을 강조하여 현대 슈퍼컴퓨팅 아키텍처를 보다 현실적으로 평가할 수 있도록합니다. 특히, 참조 HPCG 구현의 메모리 병목 커널인 SymGS (Symmetric

Gauss-Seidel) 루틴과 대역폭 제한을 받는 SpMV (Sparse Matrix-Vector Multiplication) 연산은 성능을 제한하는 요인입니다.

본 논문은 이식성 문제를 해결하기 위해 Kokkos 프로그래밍 모델을 사용한성능 이식 가능한 HPCG 벤치마크인 KoHPCG 를 소개합니다. 본 연구는 HPCG 최적화 기법에 대한 철저한 조사를 바탕으로 병목 현상과 개선 사항을 파악하는 것에서 출발합니다. 수치 정확도에 영향을 주지 않으면서 병렬확장성을 향상시키기 위한 여러 가지 SymGS 알고리즘 변형을 개발하고평가합니다.

KoHPCG 구현은 DDOT, WAXPBY, SpMV, SymGS, MG 연산을 포함한 모든 핵심 HPCG 커널을 Kokkos 로 변환하며, 메모리 관리, 병렬 실행, 실행/메모리 공간 추상화를 위해 Kokkos::Views 를 사용하여 아키텍처에 구애받지 않는 성능 이식성을 달성합니다. Intel Xeon Phi (KNL) and Xeon Skylake (SKL) 시스템에서 MPI+OpenMP 환경으로 최대 16개의 노드를 사용하는 다중

노드 환경에서의 확장성 실험을 통해 기존 참조 HPCG 구현 및 KHPCG 와 같은 이전 Kokkos 기반 구현보다 유의미한 성능 향상을 보여줍니다.

본 연구의 주요 기여는 다음과 같습니다: (1) HPCG 최적화 기술 및 병목 현상에 대한 철저한 분석, (2) 병렬 확장성을 개선하는 새로운 SymGS 알고리즘 변형, (3) Kokkos 를 활용한 완전한 성능 이식 가능한 HPCG 구현, (4) 인텔 아키텍처를 대상으로 한 포괄적인 성능 평가. 이 연구는 다양한 시스템에서 현실적인 성능 평가를 가능하게 하는 견고하고 확장 가능한 벤치마크 프레임워크를 HPC 커뮤니티에 제공함으로써, 성능 이식 가능한 HPCG 개선의 기반을 마련합니다.

키워드: 고성능 컨주게이트 그래디언트(HPCG), 대칭 가우스-자이텔(SymGS), 반복 해법, 병렬 컴퓨팅, 성능 최적화, 성능 이식성, Kokkos, 멀티그리드(MG), 고성능 컴퓨팅(HPC).

#### **CHAPTER 1. Introduction**

The High-Performance LINPACK benchmark (HPL) [1] has been utilized to measure supercomputer performance since the 1990s. Primarily employed to solve the dense linear algebraic equations. Despite HPL's longstanding reliability as a standard, modern supercomputers and emerging applications have exposed its bounds. HPL measures only peak performance, however it fails to accurately represent the performance of modern applications. These applications are sophisticated and require optimal coordination of different components within the computer system.

High-performance computing (HPC) utilizes the High-Performance Conjugate Gradient (HPCG) [2–5] as an entirely different benchmark for evaluating and comparing the performance of modern supercomputers. The HPCG benchmark utilizes the conjugate gradient method, which function on sparse matrices. A sparse matrix is a matrix characterized by a significantly large number of zero elements in comparison with non-zero elements. HPCG specifically accounts for deficiencies of HPL and presents a complement to the well-established HPL benchmark. HPCG more accurately measures the performance of modern applications by evaluating their capacity to deal with complex problems. HPCG evaluates the coordination of all components of the computing system, including memory bandwidth, computational

capability, interconnect network efficiency, and overall system synchronization. HPCG is a benchmark that more accurately represents the performance of modern, practical, and real-world applications.

HPL solves the linear equations in dense matrices using Gaussian elimination with partial pivoting, whereas HPCG concentrates on partial differential equations (PDEs) and solves linear systems of equations in sparse matrices, discretized using 27-point stencils for three-dimensional elliptical PDEs. The HPCG reference implementation uses the preconditioned conjugate gradient (PCG) algorithm in conjunction with the multigrid method (MGM). The ability of HPCG to evaluate different components of the system provides it an advantage over HPL. The recent development of Exaflops (10<sup>18</sup> flops) supercomputers makes the use of HPL to measure system performance less attractive for practical applications.

Kokkos [6] is a C++ library designed to enhance performance portability across diverse hardware architectures. These architectures encompass central processing units (CPUs), graphics processing units (GPUs), and other novel platforms. Besides offering abstractions for parallel execution and data management, it allows developers to produce code that is efficient and portable, without having to deal with the complexities that are specific to the hardware architectures. Kokkos is compatible with various backends, including CUDA, HIP, SYCL, OpenMP, and C++ threads, facilitates seamless transitions between different execution environments. Kokkos Kernels offers a compilation of performance-optimized routines. These routines comprise of sparse and dense linear algebra, batched operations, and graph algorithms. All of these routines are formulated according to the Kokkos programming model. The interplay of these two factors enables developers to construct high-performance applications that align with the progressively evolving

paradigm of HPC.

#### 1.1 Motivation

The foundation of HPCG is the Preconditioned Conjugate Gradient (PCG) algorithm, which depends on essential computational kernels: Sparse Matrix-Vector Multiplication (SpMV) and Symmetric Gauss-Seidel (SymGS). These kernels are memory bound, with SymGS identified as the main performance bottleneck owing to its inherently sequential nature and data dependencies. This bottleneck significantly restricts scalability and impacts the effective use of modern hardware, where computational throughput outweighs the available memory bandwidth.

Over the past decade, numerous researchers have proposed methodologies to improve the performance of SymGS across various hardware platforms, including CPUs, GPUs, MICs, and FPGAs. However, these efforts have predominantly resulted in architecture-specific optimizations that require significant optimization and are not easily portable across diverse systems. The increasing diversity of HPC systems renders the absence of performance portability a major limitation.

A notable attempt to address this issue was the development of KHPCG [7, 8], a Kokkos-based variant of HPCG aimed at delivering performance portability through hardware abstraction. The Kokkos programming model [6, 9, 10] accommodates multiple backends, including CUDA, HIP, SYCL, and OpenMP, allowing applications to operate on diverse platforms without requiring the modification of architecture-specific code. Although KHPCG an important step forward but it was suffered from several limitations, including limited parallelism (support for a single MPI rank), suboptimal performance, and numerical instability, especially in the multicolor implementation of SymGS. The report [11] emphasized the main

problems in the practical implementation of KHPCG.

These challenges highlight a clear need for an effective solution. The motivation behind this thesis arises with the goals in mind, as follows:

- Addressing the performance bottleneck caused by the SymGS routine in the HPCG benchmark through the development of parallel variants of SymGS.

- Porting the core HPCG computational kernels to the Kokkos programming model to facilitate portability.

- Providing the HPC community with a scalable, efficient, and performance-portable implementation of the HPCG benchmark capable of functioning across diverse architectures.

#### 1.2 Problem Statement

Although HPCG is valuable for simulating realistic application behavior, its performance is considerably constrained by memory-bound kernels, especially SymGS and SpMV operations. The existing reference implementation of SymGS in HPCG is sequential, presenting two significant issues:

- It fails to properly exploit the parallel processing capabilities of modern CPUs, GPUs, and other accelerators.

- It does not scale efficiently with increasing core counts or across different architectures.

Thus, there is a need to redesign the SymGS routine for parallel execution without compromising its convergence properties and to integrate this within a performance-portable framework to support future computing environments.

#### 1.3 Research Objectives and Contributions

The primary objective of this thesis is to develop a high-performance and performance-portable implementation of the HPCG benchmark, focusing particularly on optimizing the SymGS kernel. The specific goals are as follows:

- Analyze the limitations of the current SymGS implementation in the HPCG benchmark.

- Investigate existing parallelization strategies for SymGS based on graph theory.

- Design and implement a parallel and scalable SymGS algorithm suitable for various hardware architectures.

- Integrate the new SymGS implementation into the HPCG benchmark using the Kokkos framework [6] for performance portability.

- Evaluate the performance of the proposed solution across multiple architectures including CPUs and GPUs.

#### **Key Contributions:**

- A thorough study and classification of SymGS optimization strategies for HPCG.

- Development of new parallelized variants of the SymGS without compromising the numerical stability while improving performance.

- The optimized SymGS method is integrated to a Kokkos-based HPCG benchmark implementation so that it can be used on multiple platforms.

- Empirical evaluation of the proposed implementation on Intel Xeon Phi (KNL)

and Xeon Skylake (SKL) systems to demonstrate performance improvements

and scalability.

#### 1.4 Thesis Organization

The remainder of this thesis is organized as follows:

#### · Chapter 2. Background

This chapter introduces the foundational concepts and tools you need to know in order to understand the rest of the thesis. It includes:

- HPCG: Overview of the High Performance Conjugate Gradient benchmark.

- Kokkos: Introduction to the Kokkos programming model and its role in performance portability.

- SymGS: Explanation of the Symmetric Gauss-Seidel routine and its significance in HPCG.

#### • Chapter 3. Literature Review

Examines prior research efforts and developments, concentrating on:

- HPCG: Implementation details, its evolution and adoption. Its

optimization constraints as some changes are allowed, but the authors

who developed HPCG imposed some restrictions and insisted that those

parts of the benchmark should not be modified.

- SymGS: Optimizations and limitations that have been reported in previous work.

- Kokkos-Based Implementation: Review of Kokkos integration into

HPCG and related performance-portable efforts.

#### · Chapter 4. Techniques and Trends in HPCG

Explores broader patterns and practices used in optimizing HPCG, such as:

- Parallelization Strategies: Different parallelization strategies adopted

by other researchers to improve the architecture-specific performance.

- Data Layout and Storage Formats: Different data storage formats and their impact.

- Open Challenges: Technical issues in the pursuit of scalable and portable HPCG.

#### · Chapter 5. SymGS Variants

Details the development and parameters selection of:

Our Developed SymGS Variants: Present the concept and algorithmic details of our effort to parallelize the SymGS and conduct a comparative analysis of these variants.

#### • Chapter 6. Performance-Portable KoHPCG

Presents the design and build details of a Kokkos-based portable HPCG implementation that includes our optimized SymGS variant.

#### • Chapter 7. Conclusion and Future Work

Summarizes the thesis contributions and outlines directions for future research.

## CHAPTER 2. Background

#### **2.1 HPCG**

HPCG is a new benchmark more relevant to real application for HPC systems than other benchmarks like HPL. Its primary objectives are to achieve the ability to estimate the system performance for the target application by mirroring the computational behaviors in actual environments and contribute to enhancing computer systems that address practical use cases, to complement the measurements that show the theoretical potential of the system. The HPCG benchmark measures supercomputer performance, providing a more realistic measure than the HPL benchmark [12].

#### 2.1.1 Preconditioned Conjugate Gradient Method

Conjugate Gradient (CG) method is a numerical iterative solver used to solve linear systems, and the convergence rate of the CG method is measured to evaluate systems performance. The HPCG benchmark depends upon the Preconditioned Conjugate Gradient (PCG) algorithm [12], which is an iterative computational technique helpful when solving large size sparse linear system of equations [2].

Algorithm 1 Preconditioned Conjugate Gradient (PCG) begins by initializing

#### Algorithm 1 Preconditioned Conjugate Gradient (PCG)

```

1: Input: Matrix A, vectors b, initial guess x, tolerance (\epsilon), max iterations k_{\text{max}}

2: Output: Approximate solution vector x

3: Set: x_0

\triangleright Set initial guess: x_0

4: r_0 = b - A \cdot x_0

> Set initial search direction

5: p_0 = r_0

6: normr_0 = ||r_0||_2

7:

for k = 1 to k_{\text{max}} do

z_k = MG(A, r_k)

> Compute preconditioned residual

\operatorname{rtz}_k = r_k \cdot z_k

9:

Ap_k = A \cdot p_k

10:

\alpha_k = \frac{\operatorname{rtz}_k}{p_k \cdot Ap_k}x_{k+1} = x_k + \alpha_k p_k

11:

12:

□ Update solution

□ Update residual

r_{k+1} = r_k - \alpha_k A p_k

13:

if ||r_{k+1}||_2/\text{normr}_0 < \epsilon then

14:

break

15:

end if

16:

\beta_k = \frac{\operatorname{rtz}_{k+1}}{\operatorname{rtz}_k}

17:

p_{k+1} = z_{k+1} + \beta_k p_k

▶ Update search direction

18:

19: end for

```

an approximate solution  $x_0$  and compute the initial residual  $r_0=b-Ax_0$ , which estimates the error in the initial guess, and the direction of search is initially set as the residual,  $p_0=r_0$ , and the algorithm iterates to update residual and search direction to reach for the solution. In each iteration a multigrid preconditioner is used to improve the convergence, then a dot product and a matrix-vector multiplication are performed to compute the step size  $\alpha_k$ , and it determines to move along the search direction. The solution and then the residual are updated to recalculate the remaining error. If the error is sufficiently small, the iteration process stops algorithm to perform, when it check for convergence by comparing the current residual against a given  $\epsilon$ . If not, the search direction is updated, to ensure it remains conjugate to the previous directions, and the process repeats. With appropriate preconditioning, this iterative approach allows the PCG method to efficiently solve large sparse systems of equations. HPCG

is primarily relies on the performance of the SpMV and SymGS. HPCG solves a sparse linear equation with a simple additive Schwarz using the PCG algorithm [2].

#### 2.1.2 HPCG Execution Flow Process

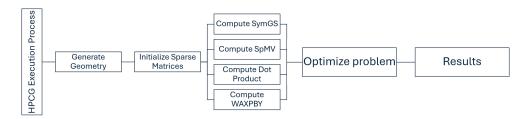

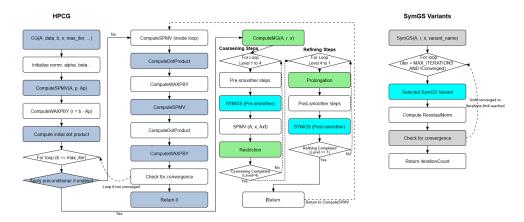

The HPCG benchmark is designed to simulate real-world computation patterns usually found in scientific/engineering applications. Its execution flow as shown in Figure 2.1 begins with allocating for the local sub-domain of each MPI process and the geometry setup, which divides the problem domain for parallel computing. Then, initializes sparse matrices and prepares main data structures such as the matrix A, solution vector x, and right-hand side vector b. Key computational operations are **Compute SymGS**, which performs SymGS iterations to approximate the solution of the sparse system, while **Compute SpMV** called to accomplish the sparse matrix-vector multiply, **Compute Dot-Product** computes the vector-vector dot products, and **Compute WAXPBY** does the weighted vector adds. Finally, users may implement their optimization routines using the **OptimizeProblem** function provided in the reference implementation. Once the iterative process is completed, results produces a report consisting of timing information, flops, memory bandwidth, and validation information.

The core computational kernels participating in the HPCG benchmark are Dot Prodeuct (DDOT), WAXPBY, SymGS, SpMV, Restriction and Prolongation operations, which are explained in detail in Section 2.1.6.

HPCG forms the problem setup then a symmetric positive definite matrix is created from Compressed Sparse Row (CSR) format [2]. Such an approach makes use of memory and computations in the most efficient manner possible, and the benchmark really tests the capabilities of a machine. The amount of data in the matrix is

Figure 2.1 HPCG Execution Process Flow

designed to optimally fit the machine's capacity to conduct an exhaustive assessment of its performance. HPCG benchmark implies the local SymGS preconditioner. Whereas this preconditioner helps in the reduction of the matrix and so helps in faster convergence in PCG algorithm. The matrix is divided into lower and upper triangular matrices; this allows the preconditioner to gradually improve the solution making it functionally efficient. Also, the benchmark requires verification and/or validation processes, computation of pre/post conditions, and invariants. Convergence tests and comparison with the reference kernels were employed to check the accuracy of the computation to assure that the results obtained are consistent. HPCG benchmark replicates the actual application workloads and uses multiple iterations. Numerical results obtained at each iteration are checked with expected answers for verification and cache is cleared before each iteration. It eliminates cases of false popularity from cache usage as well as ensures an impartial evaluation of the system. Finally, HPCG produces a report consisting of timing information, flops, and validation computations. System configuration is documented throughout this report and may be critical in understanding benchmark performance. This makes HPCG benchmark comprehensive and fair at the same time for HPC systems evaluation.

#### 2.1.3 Problem Setup in HPCG

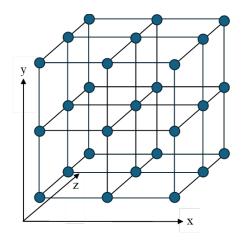

Figure 2.2 shows a 27-point stencil 3D in HPCG benchmark designed to solve the linear system of equation:

$$A \cdot x = b$$

.

where A is a sparse matrix of size  $n \times n$ , x is an unknown vector of size n, b is a known vector of size n.

Figure 2.2 27 point stencil in HPCG

It approximate the values of the solution vector  $\boldsymbol{x}$  using the PCG algorithm, which is an iterative computational technique helpful when require to solve the system of large and sparse linear equations. The benchmark is using the Poisson equation discretized on a 3D cubic domain with homogeneous Dirichlet boundary conditions. This benchmark performs domain decomposition, using an additive Schwarz method. Each subdomain is further preconditioned with a SymGS, one of the core numerical kernels of HPCG.

#### 2.1.3.1 Sparse Matrix Representation

The matrix A is sparse and most of its entries are zero. In the context of the three-dimensional grid, every cell of the grid is connected with its neighbor, which gives the nonzero entry of the matrix A. The 27-point stencil, in a 3D discretization connects it with 26 immediate neighbours, including the 6 face neighbours, 12 edge neighbours, and 8 corner neighbours. This leads to a sparse matrix format where there is at most 27 non-zero value in each row represents each grid point with the current point and its neighbors.

#### 2.1.3.2 Domain Decomposition and Process Layout

A 3D grid is the problem domain, which is sub-divided into smaller subdomains. These subdomains are distributed among multiple MPI processes to parallelize the computation.  $N_x$ ,  $N_y$  and  $N_z$  are the dimensions of the local sub-domain and in the process layout  $NR_x$ ,  $NR_y$ , and  $NR_z$  are number of MPI processes in x, y and z directions, respectively. The global domain size is thus given by  $(NR_x \times N_x) \times (NR_y \times N_y) \times (NR_z \times N_z)$ , and the total computation is divided among the  $NR_x \times NR_y \times NR_z$  MPI processes, each handling a subgrid of the overall domain.

#### 2.1.3.3 Stencil Operator

The 27-point stencil operator, illustrated in the Figure 2.2, demonstrates how a central grid point and its immediate neighbors are coupled in a 3D grid. Each dot represents a grid point, and edges indicate how each point interacts is coupling with its neighbors. This stencil is one of the most important factors in the HPCG benchmark because the sparse matrix operations rely directly on this stencil due to the definition of the structure of matrix A.

The HPCG benchmark is designed to emulate the behavior of real-world applications that solve large, sparse linear systems on 3D grids. At the center of defining the sparsity pattern of matrix A is the 27-point stencil operator, and efficient computation is divided among several MPI processes to leverage parallelism in high performance computing environments. This leads to a sparse matrix format where there is at most 27 non-zero value in each row represents each grid point with the current point and its neighbors.

### 2.1.4 Properties

The HPCG benchmark constructs a 3D partial differential equation model problem and uses preconditioned conjugate gradient iterations on the sparse linear system [4]. The characteristics are defined by input parameters, but some constraints are applied at the setup stage. The benchmark builds up a sparse linear system that is distributed with 27-point stencil for each of the grid points. This results in a matrix with specific properties [4, 5]:

#### 1. Nonzero Entries Per Row:

Nonzero entries per row =

$$\begin{cases} 27, & \text{for interior points} \\ 7 \text{ to } 18, & \text{for boundary points} \end{cases}$$

#### 2. Matrix Properties:

The matrix is **positive definite**, **symmetric**, and **non-singular**.

$$A = \begin{bmatrix} a_{11} & a_{12} & \cdots & a_{1n} \\ a_{21} & a_{22} & \cdots & a_{2n} \\ \vdots & \vdots & \ddots & \vdots \\ a_{n1} & a_{n2} & \cdots & a_{nn} \end{bmatrix}$$

where  $A^T = A$  (symmetric),  $\forall x \neq 0$  when  $x^T A x > 0$  (positive definite), and  $\det(A) \neq 0$  (non-singular).

#### 3. Exact Solution Vector:

The exact solution vector x is known, with all elements equal to 1.0.

### 4. Matching Right-Hand-Side Vector:

The right-hand-side vector b is constructed to match the exact solution.

$$A \cdot x = b$$

.

### 5. Initial Guess:

The initial guess vector  $x_0$  is selected with all zeros.

### 2.1.5 Optimization Constraints

In the reference implementation of HPCG, some optimizations are allowed, but the authors who have developed HPCG, imposed some limitations and insisted for not modifying those aspects of the benchmark [4].

### 2.1.5.1 Allowed Optimizations

**Mesh Partitioning/Reordering** optimization is in fact the reorganization of the mesh points to help in the minimization of overhead that may arise in cases of data distribution between different processors and also help in the optimal use of cache in a hierarchical memory system.

User defined data structures eliminating different levels of abstraction and creating custom data structures tailored to the computational kernels can enhance memory access patterns and data locality and enhance the computational performance. When data structures are well defined then there is improvement in the efficient usage of memory.

**System-Specific Communication Infrastructure Optimization** can lead to the overall performance improvement. Utilization of specific network hierarchies and topologies tailored for hardware characteristics helps in improving the communication strategies.

**Advance MPI communication** if different types of MPI features are used, for example synchronization using neighborhood collective is an efficient communication pattern for specific application need [13]. Advance MPI features of course decreases the communication overhead and able to share data in the more efficient way which leads to the scalability on the large core counts.

**Data storage format** changes are permitted to sparse matrix data structure to improve the memory access but these changes for SpMV and SymGS kernels must not eliminate the indirect addressing of the input vector.

Computational Kernel Optimizations must have the same mathematical preconditioner, which must be capable of stressing the different component of

the system. Therefore the computational kernels coding which required special consideration for optimizing are:

- Compute DOT Product

- Compute WAXPBY

- Compute SpMV

- Compute SymGS

- Compute MG

#### 2.1.5.2 Not Allowed Optimizations

**Basic Conjugate Gradient (CG) Algorithm** optimization by means of different variants of the CG method avoiding some challenging aspects of the classical algorithm. Some examples of the prohibited variants are Reordered conjugate-gradient methods [14–18] and Pipelined conjugate-gradient methods [19,20]

**Matrix Data Properties** with prior knowledge concerning the pattern of sparsity, or the structure, or exploiting the discretization symmetry of matrix, and domain dimensionality information.

**Spectral Properties** information exploitation for the utilization of the optimal preconditioners or acceleration of its iterations unrealistically based on the known spectral properties of the matrix.

**Data Representation Simplifications** by applying the infrequency of the matrix pattern as regular or using near-regularity to the pattern. Reduction in the storage requirement by changing the defined precision or exploiting the symmetry in the data

is also prohibited.

**Other modifications** such as the optimizations which bypass the objectives of the benchmark are generally not permitted.

#### 2.1.6 Core Kernels in HPCG

In HPCG, for solving  $A \cdot x = b$ , a PCG algorithm is used as described in Algorithm 1. These algorithms of the core kernels are presented in the simplest way to understand the task performed by these kernels, but the optimization of these kernels is not as simple as they seems simple in these algorithms because the data dependencies significantly complicate the optimization, when they use within the PCG. Section 3.1 summarize the efforts put in by researchers towards addressing the challenges in optimizations.

### 2.1.6.1 Dot Product (DDOT)

$$\alpha = x \cdot y \tag{2.1}$$

where  $\alpha$  is scalar and the x, y are vectors.

DDOT calculates the scalar result of two input vectors x and y, each of length n.

#### 2.1.6.2 WAXPBY

$$w = \alpha \cdot x + \beta \cdot y \tag{2.2}$$

where  $\alpha$  and  $\beta$  are the scalar values, x and y are input vectors, and w is the resultant vector.

WAXPBY is the weighted addition of two vectors x and y (scaled vector  $\alpha x$  plus a scaled vector  $\beta y$ ), also known as vector vector coefficient multiplication [21]. An

abbreviation come from the operation it performs as mentioned in equation 2.2. The operation takes the vector x, scales it by  $\alpha$ , and the vector y, scales it by  $\beta$  and then add these two scaled vectors together and get the resultant vector w.

### 2.1.6.3 Sparse Matrix-Vector Multiplication (SpMV)

$$y = A \cdot x. \tag{2.3}$$

SpMV computes the product of a sparse matrix A with a vector x to produce a vector y. The reference implementation employs the Compressed Sparse Row (CSR) data format. However, there are various data formats discussed extensively in literature by many researchers. Some of the most common sparse matrix data formats are also mentioned in Section 4.1.

#### 2.1.6.4 Symmetric Gauss-Seidel (SymGS)

The Symmetric Gauss-Seidel (SymGS) method is an effective iterative solver for sparse linear systems of the form:

$$A \cdot x = r, \tag{2.4}$$

where A is an  $n \times n$  sparse symmetric positive definite (SPD) matrix, r is the residual vector, and x is the solution vector. The matrix A is decomposed into three components:

- L: the strictly lower triangular part of A,

- U: the strictly upper triangular part of A,

- D: the diagonal matrix containing the diagonal entries of A.

The SymGS algorithm consists of two main phases forward and backward sweeps, applied sequentially during each iteration. These steps aim to update the solution vector by attenuating high-frequency errors.

**Forward Sweep:** In the forward sweep, the updated solution is obtained using the lower triangular and diagonal parts of *A*:

$$(L+D) \cdot x^{(k+1)} = r - U \cdot x^{(k)},$$

(2.5)

where  $x^{(k)}$  is the solution at the k-th iteration.

**Backward Sweep:** The backward sweep then refines this update using the upper triangular and diagonal components:

$$(U+D) \cdot x^{(k+1)} = r - L \cdot x^{(k)}.$$

(2.6)

**Residual Computation:** The residual vector r is computed as:

$$r = b - A \cdot x^{(k)}. (2.7)$$

**Role in HPCG:** In the HPCG benchmark, SymGS serves as a smoother within the multigrid preconditioner. Its primary objective is to suppress high-frequency error components that arise during iterative solution of the linear system, in the PCG method.

However, due to the inherent data dependencies in both the forward and backward sweeps, parallelization of SymGS is challenging. These dependencies limit concurrent updates to the solution vector, making SymGS less scalable on modern

multi-core and many-core architectures.

#### 2.1.6.5 Multigrid V-cycle (MG)

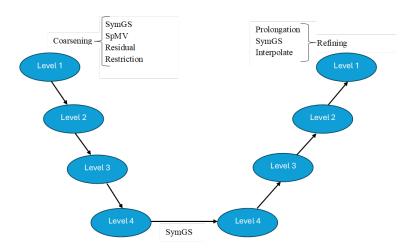

Multigrid V-cycle is among the most effective iterative methods in solving large systems of linear equations. The method take advantage of mulltiple levels of grid resolutions by recursively moving between finer and coarser grids for better convergence by addressing high-frequency and low-frequency errors. This multigrid method (MGM) accelerates the convergence of coarser grids by reducing the errors efficiently, compared to conventional iterative methods.

${f MG}$  takes a matrix A and a vector r as input and initializes a solution vector x to zero. If multigrid data available for the matrix A, the algorithm applies pre-smoothing using iterative solver SymGS. This helps to reduce the high-frequency errors that are present in the initial guess provided for x. The smoothing step is next followed by the computation of the residual. This residual is taken as the error in the current approximation. The residual is then restricted to a coarser grid, and on the coarser grid the low-frequency errors could be resolved. The restriction reduces the size which makes the solution faster to solve. The algorithm then solves the problem on the coarser grid recursively. This recursion allows the algorithm to repeat the same multigrid steps at each coarser level where the problem becomes small enough to solve easily. Once solved at the coarsest level, the solution is prolongated back to the finer grid. This prolongation step interpolates the coarser grid solution back to the finer grid, to enable it for further refinement of the solution.

Then post-smoothing is done on the finer grid by using SymGS again. This post-smoothing step will ensure that any high-frequency errors, that may be generated by the prolongation can reduced to get an accurate solution. If multigrid data is not

exist, then algorithm falls back to applying the SymGS smoother directly for solving the system without multigrid coarsening or prolongation. This fallback ensures that, even in the absence of multigrid the algorithm could still solve. The preconditioner utilized in HPCG is a V-cycle from the geometric multigrid methods. The total number of V-cycle levels are hard coded to 4 in the reference implementation of the HPCG as shown in Figure 2.3.

Figure 2.3 Geometric multigrid V-cycle preconditioner in HPCG

### 2.2 Kokkos EcoSystem

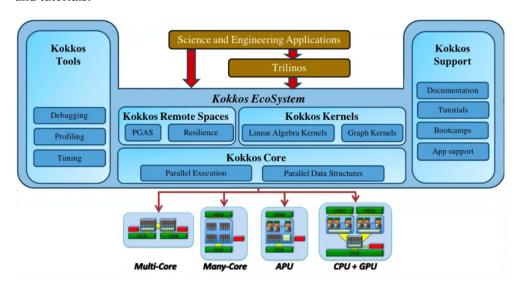

Kokkos [6, 9, 10] is a C++ template library and programming model that makes it possible to run programs on different architectures by abstracting parallel execution and data management and mapping high-level constructs onto backends like CUDA, HIP, SYCL, OpenMP, and threads. Kokkos is engineered to address complex node architectures featuring N-level memory hierarchies and various execution resource types. Its main abstractions are execution and memory spaces, execution patterns and policies, memory layouts, and these traits make it possible to specialize at compile

time for the target hardware. Kokkos provides a complete ecosystem as shown in Figure 2.4 for performance portability which includes math kernels, tools for debugging, profiling, and tuning, and community support through documentation, and tutorials.

Figure 2.4 Overview of the Kokkos ecosystem including tools, core components, remote spaces, and kernel libraries. Adapted from [22].

Kokkos was initially created at Sandia National Laboratories as part of the Exascale Computing Project to fulfill the requirement for a unified codebase that can target CPUs, GPUs, and other accelerators without necessitating algorithmic rewrites. It decouples algorithmic intent from hardware specifics by providing compiletime abstractions for parallel execution and memory management.

### 2.2.1 Programming Model

Core Abstractions: The programming model is based on abstractions: execution spaces, execution patterns, execution policies, memory spaces, memory layouts, and memory traits.

- Execution Spaces: Execution spaces (like CUDA, HIP, OpenMP, and Threads) tell where parallel kernels run. This lets code change according to target architecture just by changing template parameters.

- **Memory Spaces:** Specify where the data is stored (like CudaSpace or HostSpace).

- Execution Patterns: Parallel constructs like parallel\_for, parallel\_reduce, and parallel\_scan.

- Execution Policies: Control execution behavior, such as range and team policies.

- **Memory Layouts:** Define the data arrangement in memory (e.g., LayoutLeft, LayoutRight).

- Memory Traits: Define properties like unmanaged or atomic access.

### 2.2.1.1 Sample Code Example

This simple 1D vector addition implementation show Kokkos programing structure for portable execution across backends for example with OpenMP for CPUs, CUDA for GPUs.

#### **Kokkos Example (Portable)**

```

Kokkos::parallel_for("VecAdd",

Kokkos::RangePolicy<>(0,N),

KOKKOS_LAMBDA(const int i) {

C(i) = A(i) + B(i);

});

```

The Kokkos example hides the details of managing threads at a low level, so the same code can run on both CPUs and GPUs by choosing the right execution space at compile time.

### 2.2.2 Packages/Repositories

The Kokkos EcoSystem as shown in Figure 2.4 has a number of packages/repositories, which are listed below.

- Kokkos Core: The Core library implements the above mentioned abstractions, assigning tasks to backends and controlling data lifecycle without causing runtime overhead.

- **Kokkos Kernels:** Kokkos Kernels is a library that works with Kokkos and provides sparse and dense linear algebra routines, batched BLAS/LAPACK, and graph algorithms. It works well on both CPUs and GPUs.

- Kokkos Remote Spaces: Remote Spaces adds a Partitioned Global Address Space (PGAS) model to Kokkos, which lets you use distributed-memory data structures with resilience capabilities.

- Kokkos Tools: The Tools interface offers mechanisms for debugging,

profiling, and autotuning frameworks, presenting comprehensive runtime

information through a standardized callback APIs.

• **Kokkos Support:** Comprehensive documentation, tutorials, and bootcamps guide users in integrating Kokkos into their projects via CMake and GitHub repositories.

# **CHAPTER 3.** Literature Review

This chapter provides an overview of the research that has already been done on optimization strategies for the HPCG benchmark. This chapter discussed architecture-specific optimizations, which cover CPUs, GPUs, hybrid systems, FPGAs, GraphBLAS and performance-portable frameworks like Kokkos. Chapter 4 contains details of sparse matrix data formats and parallelization optimization strategies discussed in the literature review.

# 3.1 HPCG Optimization Techniques

In HPCG, the most time-consuming kernel is SymGS, followed by SpMV because of its memory-bound nature. The optimization of HPCG primarily focuses on the optimization of these two main kernels. For optimization of SpMV, effective strategies are domain decomposition, parallelization, and the utilization of the efficient storage format. For SymGS optimization, parallelization techniques and hardware-specific tuning applied by the researchers are summarized in the following subsection. In both kernels, the hybrid parallelization approaches combine MPI (distributed memory) and OpenMP (shared memory) parallelization schemes. Hardware-based parallelization, such as vectorization through SIMD instructions and task offloading on GPUs or FPGAs, also significantly enhances the

performance of these kernels. Other than these, task load balancing, communication computation improvement, and cache-friendly data reordering techniques are also discussed literature. The multigrid method offers another avenue for optimization by subdividing the problems and solving them at multiple levels. The effectiveness of the optimization using these techniques necessitates the careful tuning of the problem based on the specific hardware architecture characteristics. Successful optimization of the HPCG benchmark required a careful combination of these techniques tailored to the target system and the properties of the sparse matrix used.

In this section, we group the optimization techniques discussed in the reviewed papers by architecture and year-wise. Since the introduction of HPCG in 2013, several optimizations have been done regarding different architectures.

### 3.1.1 CPU-Based Systems

### 3.1.1.1 Intel Architecture - IA

In 2015 [23] presented the updates on their intel-based work [24], which further tested on single and multi-node with the enhancements introduced in HPCGv3.0. They also focused on software upgradation such as optimized sparse matrix operations in the Intel Math Kernel Library (MKL) [25] and the open source SpMP library [26] for sparse matrix pre-processing and optimization of multi-grid implementation to enhance the performance of HPCG. The upgradation for HPCGv3.0 with these optimizations in the GenerateProblem and SetupHalo routines reduced the overhead to less than 3% and 4% on Haswell (HSW) and Knights Corner (KNC) architectures, respectively.

**In 2016** [27] expanded upon the previous work [24] of the authors, optimized HPCG for Intel Xeon and Xeon Phi processors using techniques like point-to-point

synchronization, loop fusion, and hybrid parallelization schemes. The novelty of this work lay in the fusion of GS and SpMV, and these optimization techniques significantly reduced the amount of data transfer from memory by enabling data to be reused from the cache. [28] optimized HPCG for a CPU+MIC platform, with techniques like offload programming, vectorization, and parameter tunings. The author applied different optimization techniques, including the integration of an offload programming mode to use the Intel Xeon Phi coprocessors for computationally intensive kernels, vectorization using the Intel compiler auto-vectorization options, and parameter optimizations to find the best matrix size for MIC architecture. They were parallelized and optimized the four main kernels of the HPCG. Their approach allowed the CPU to handle less parallelizable tasks, and the MIC co-processors managed to execute heavily parallelizable routines. Further, the authors highlight the impact of heat dissipation from the devices on performance stability and develop an intelligent dynamic cooling solution for the MIC coprocessors to keep them at optimal temperatures and maintain their performance stability. They demonstrated that heat management is also critical for achieving stable performance on MIC coprocessors. They achieved significant speedup over the reference implementation.

In 2024 [29] optimized implementation primarily developed for ARM-based systems but also tested on an Intel Xeon system. They also tested their techniques on both single nodes and distributed cluster environments, scaling up to 256 nodes and 16,384 cores with 2048 MPI processes. The results showed nearly linear scalability and improved performance, particularly when incorporating asynchronous communication strategies.

#### 3.1.1.2 Arm-Based Architectures

In 2019 [30, 31] presented the profiling of HPCG on an Arm-based platform Cavium ThunderX2. Demonstrated an optimized implementation of the HPCG benchmark with an emphasis on shared memory parallelization using OpenMP. In addition to a dynamic slicing technique for adaptive block geometry, the authors employed two primary optimization strategies: multi-color reordering and block multi-color reordering of the SymGS preconditioner. The optimizations presented in this paper [31] are identical to those that have already been discussed in the technical report [30]. The strategies outlined in this paper were specifically developed for the ARMv8.1 Cavium ThunderX2 processor, which features a shared memory architecture.

In 2023 [32] implemented a new HPCG based on the ALP/GraphBLAS [33] and tested it on ARM Kunpeng (920-4826) up to 7 nodes ARM cluster. It had scalability issues in distributed settings. The objective of this work was to leverage the algebraic abstraction and optimization capabilities of ALP/GraphBLAS [34], which is a C++ variant of GraphBLAS called ALP. The authors proposed a new implementation of HPCG based on ALP/GraphBLAS [35] and conducted the evaluation of its performance on both shared and distributed memory systems. The SymGS smoother was replaced with a Red-Black Gauss-Seidel (RBGS) to facilitate parallelism, and restriction and refinement operations were implemented as matrix-vector multiplications as the key design changes. Their implementation [35] outperformed in shared memory experiments on x86 and ARM architectures and encountered significant scalability limitations in distributed systems, compared to the reference implementation, mainly due to the communication overheads and the inability of GraphBLAS to efficiently manage data distribution.

In 2024 [36] focused on the theoretical development of the optimization techniques, and another paper [29] expanded on the practical implementation and provided the performance evaluation across different applications in detail. These two papers are closely related, and the research presented focused on optimizing the Multi-Grid Preconditioned Conjugate Gradient (MGPCG) method [37], which was subsequently applied to the HPCG benchmark. In this research, the authors developed novel techniques to optimize the SymGS and a block multi-color (BMC) scheduling method with point-to-point synchronization to improve the parallelism and the load balance. [29] tested their optimizations on Arm-based platforms, evaluated their optimized HPCG implementation, and compared them with vendor-tuned HPCG implementations on three different systems: Phytium 2000+, Kunpeng 920, and Thunder X2 ARMv8.

#### **3.1.1.3 K** Computer

In 2016 [38] presented the optimization on the K computer, focused particularly on single-node performance optimization of the HPCG benchmark, with several optimization techniques tailored to take advantage of the K computer's architecture. The authors utilized memory layout reorganization to achieve sequential memory access, which reduced the cache misses and improved its throughput. They also introduced data access improvements by aligning loop directions to optimize data locality and improve cache misses. Parallelization was done using multithreading and coloring methods to eliminate data dependency. Additionally, a blocked coloring technique was employed to preserve data locality within blocks for efficient multithreading of the SYMGS kernel, resulting in a substantial improvement in cache efficiency. These optimizations resulted in a significant performance improvement on the K Computers, and secured second position in November 2014 HPCG results

with 4.4% of ratio to HPL performance.

### 3.1.1.4 Sunway TaihuLight Supercomputer

In 2017 [39] presented the optimizations of HPCG on the Sunway many-core processor. The authors introduced a technique called the Hierarchical Grid (HG) algorithm, which they designed specifically for the Sunway architecture with an aim to enhance the performance of HPCG on the Sunway TaihuLight supercomputer. First, they used trivial methods to optimize the key kernels in MG V-cycle and SpMV, such as Level-Scheduling (LS) and Multi-Coloring (MC) methods used for the parallelism of the SymGS smoother. The authors proposed a new technique, HG, after realizing the limitations, such as poor locality and limited parallelism of the LS and MC. HG divided the domain into grids and subgrids mapped to the Computing Processing Elements (CPEs) cluster. They also implemented an efficient data prefetch mechanism and transfer scheme using DMA operations to manage data exchange between Management Processing Elements (MPEs) and CPEs. They used team collaborative computing to assign SpMV inner elements to CPEs and the border elements to MPE. The paper also demonstrated the scalability of their approach and comprehensive analysis of their parallel model and optimization strategies. They claimed that their approach is not only for HPCG but also for other HPC applications on the Sunway processor.

In 2018 [40] presented comprehensive optimizations, including block multi-coloring on Sunway TaihuLight to exploit hardware characteristics. The authors developed a series of optimization techniques for the HPCG benchmark on the heterogeneous many-core architecture of the Sunway TaihuLight supercomputer. Due to the high bandwidth requirements of HPCG, the main challenge was to improve the

performance of memory-bound kernels by leveraging the specific architecture of Sunway TaihuLight, which has limited memory bandwidth as compared to its computational power. The key optimizations employed in this study included a block multi-coloring approach for parallelizing the SymGS kernel, which balanced parallelism and convergence rate. Parallelism increased by dividing the computations into blocks that can fit into the LDM of CPEs while maintaining the data locality. They also implemented locality-aware layout transformations to improve data access patterns by transforming the sparse matrix storage format into ELLPACK and vectors access reordered to align with the parallelism scheme and improved the access efficiency by grouping blocks with the same color. They also developed a requirement-based data access method that mapped only necessary data for the limited local memory of each core, which reduced the data movement overhead. The required data for computations was accessed through DMA transfers, while the on-chip register communications were used to exchange data between CPEs to enhance efficiency. The researchers further decomposed operations into smaller tasks to enable fine-grain overlapping of computation and data access. Additional optimizations included code transformation, SIMD vectorization, index compression, register message combination and local data management. This work has shown that with careful optimizations used in this study, memory-bound applications like HPCG, even on architectures with challenging memory bandwidth constraints, can efficiently scale on large systems.

### 3.1.1.5 OceanLight Sunway Supercomputer

In 2021 [41] presented a series of optimization techniques intended to enable and scale the HPCG benchmark on the new generation of the Sunway supercomputer, which was equipped with over 42 million heterogeneous cores. Instead of using

multi-coloring or block multi-coloring techniques for parallelism, the authors introduced a novel two-level blocking technique to exploit parallelism in the SymGS kernel and maintain the convergence rate. This is the first paper that uses this technique to optimize the HPCG on the Sunway supercomputer. Further, they also proposed a fine-grained kernel fusion scheme that improves the data locality to alleviate the bandwidth load on local storage and another notable work was a low overhead thread coordination mechanism that transfers data between the cores. They used a simplified ELLPACK sparse matrix format for better memory alignment. These optimizations enabled to scale up to 653,760 MPI processes with 95.5% efficiency, and the optimized implementation scaled to over 42 million cores and maintained a performance of 5.91 Pflops, utilizing 73.0% of the theoretical memory bandwidth. The performance was further enhanced to 27.6 Pflops by relaxing the constraints of the HPCG benchmark. This work [42] presented effective optimization strategies for sparse linear solvers on modern heterogeneous supercomputer architectures.

#### 3.1.1.6 NEC SX-ACE Vector Supercomputer

In 2015 [43] explored various optimization techniques for HPCG benchmark on the SX-ACE supercomputer [44]. To take advantage of the architectural features of NEC SX-ACE as the vector parallel processor with a high-bandwidth memory system, the authors employed different data packing formats, including CSR, JAD [45], and ELLPACK [46] for efficient packing of sparse matrix data and found ELLPACK as most effective for its vector calculations and memory access efficiency. To eliminate data dependencies during parallelization, eight-color multi-coloring [47] and hyperplane [48, 49] techniques are also employed. They gained performance improvements using a combination of JAD+coloring, ELLPACK+coloring,

Hyperplane with selective caching in the available on-chip Assignable Data Buffer (ADB), and problem size tuning. [43] presented a series of optimizations on the SX-ACE vector supercomputer, and their optimized implementation achieved 11.4% efficiency in the case of using 512 nodes and over 30 Gflops on a single node.

In 2023 [50] presented an optimized HPCG implementation for long-vector architectures in order to achieve a performance on high-end RISC-V accelerators, mainly through kernel optimizations on enhancing memory hierarchy usage. This work applied several optimizations to the HPCG benchmark and was of great importance for the domain of HPC because it optimized the HPCG benchmark for long vector architectures, targeting specifically the NEC VE and the RISC-V vector extension (RISC-VV) platforms. The paper presented a portable and highly optimized implementation of HPCG as open source [51] to long-vector architectures.

#### 3.1.1.7 Near-Data Processing (NDP) Architecture

In 2017 [52] discussed the use of IBM Power8 near-data processors (NDPs) [53] in the optimization of HPCG and Graph500 [54] benchmark. The Graph500 benchmark focuses on breadth-first searches (BFS) in large graphs and stresses memory access and global communication. The optimizations of the Graph500 benchmark are not discussed as they are not part of the scope of this paper. For detailed information on it, please refer to the original paper [52], and the distributed Graph500 details can be found in [55]. The researchers employed a series of optimizations for the HPCG using NDP architecture. They designed a system of 8 NDPs, which contain multiple small and slow cores positioned close to the memory. The architecture also utilized a shared memory approach with coherent access across the NDPs. They replace the traditional MPI+OpenMP approach with a nested OpenMP model for parallelization,

spawning threads for each NDP and its cores. They also restructured the code to create a single parallel region encompassing the kernels instead of employing thread teams, which significantly reduced the threading overhead. They determined that a 4 KB data cache per NDP core was optimal to optimize the data locality and cache. They tested different memory access granularities and found that a 64B access granularity, combined with software prefetching, provided the best results when using DDR3200 memory. They implemented the software prefetching for Dot Product and WAXPBY kernels due to their data access patterns. However, the prefetching was more challenging due to data dependency in SpMV and SymGS kernels and the blocked multi-coloring approach for parallelism in these kernels. This study highlighted the importance of inter-NDP bandwidth, which became equally important as local memory bandwidth for the optimization of the applications. They optimized inter-NDP communication for high bandwidth and low latency, utilizing an NDP Access Point (NDP-AP) for efficient remote data access.

### 3.1.2 **GPU-Based Systems**

#### 3.1.2.1 GPU-Accelerated Systems

In 2014 [56,57] presents an optimized HPCG benchmark using CUDA for NVIDIA GPU-accelerated supercomputers, namely Titan and Piz Daint. The key optimization technique of this paper is graph coloring to enhance the parallelism of the SymGS smoother. They employed the parallel coloring technique with the local maxima [58, 59] and incorporated improvements proposed by [60]. They primarily focused on parallelizing the SymGS. They used cuSPARSE library [61] and customized CUDA-based kernels, and switched matrix data format from CSR to ELLPACK so that the memory access coalesced, which was essential for optimizing GPU

efficiency. This paper contributed to optimizing memory-bound workloads on GPUs. They benchmarked their optimized HPCG variant on both the Cray XK7 system at Oak Ridge National Laboratory (ORNL) [62] and the Cray XC30 system at the Swiss National Supercomputing Centre (CSCS) [63]. The Cray XK7 (Titan) has an AMD Opteron processor and a Gemini interconnect that has a 3D torus topology [64]. The Cray XC30 (Piz Daint) features an Intel Xeon processor and an Aries interconnect that has a dragonfly topology [65]. This was the first CUDA implementation of HPCG for GPUs, focused on parallelizing the SymGS smoother using graph coloring techniques, and their implementation achieved the fastest per-processor performance reported at that time when tested at full scale on large GPU-accelerated supercomputers like the Cray XK7 at ORNL and the Cray XC30 at CSCS.

In 2016 [66] expanded on the aforementioned research with a more comprehensive examination of the HPCG benchmark covering a broader range of GPU architectures, incorporating improved optimization techniques, and providing a more detailed analysis. Furthermore, it highlights the differences in the efficiency and prospective of GPU and CPU executions, which have not been thoroughly examined in their previous research.

### 3.1.3 Hybrid Architectures

#### 3.1.3.1 Tianhe-2 Supercomputer

In 2014 [24] is one of the first papers to have focused on the optimization of the HPCG benchmark for the multi and many-core architecture and has achieved the performance of 580 Tflops on the Tianhe-2 supercomputer. They achieved this by utilizing an approach that combines both multi-core and many-core Intel Xeon and Xeon Phi co-processors. SpMV and SymGS are the core kernels of

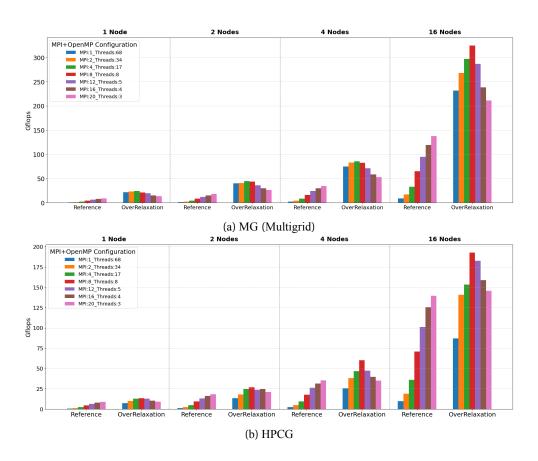

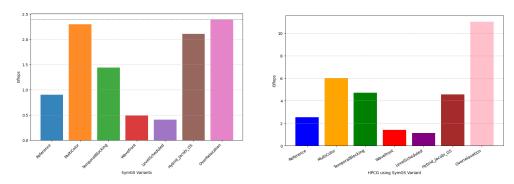

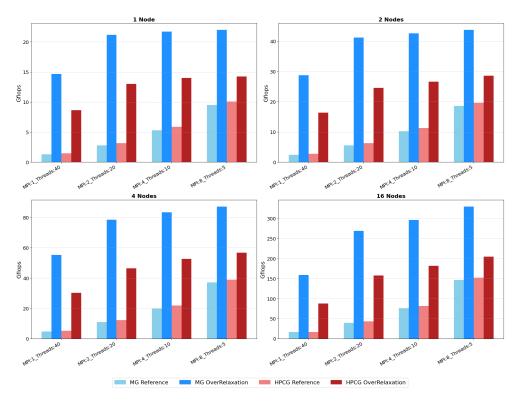

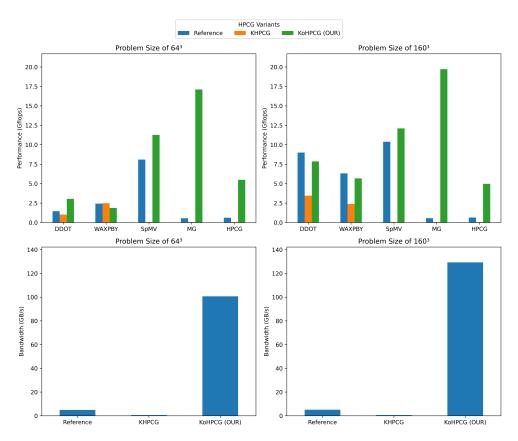

many solvers [67, 68] including HPCG. Achieving high performance of symGS smoother is particularly challenging due to its limitation in fine-grain parallelism [69] as it is inherently sequential in reference to the implementation of the HPCG. Focusing on the essential SymGS smoother, they uncover and evaluate significant limitations of the parallelism and introduced a novel hybrid approach combining the point-to-point synchronization in sparsification and block multi-color reordering technique Algebraic Block Multi-Coloring (ABMC). To optimize the data locality and memory access patterns, they also used the SELLPACK sparse matrix data format. [70] focused on improving only the CPU-based system on 6,144 nodes by utilizing techniques such as red-black relaxation, SIMDization, loop unrolling, forward-backward sweep fusion, and OpenMP parallelization, including a reformulation of the mathematical equivalent CG algorithm to minimize collective communication costs. They also replaced the default CSR format with a simplified SELLPACK format, a variant of ELLPACK [71], which improved data locality and access patterns in SpMV and SymGS. They also fused the residual computation in SpMV and restriction operation into a single subroutine in geometric multigrid v cycle inspired by the work [72]. Compared to prior work [24] on 12-core Intel Xeon processors, this optimized HPCG achieved both higher single-CPU performance and superior large-scale performance on Tianhe-2. [73] was an extension of the previous study [70] for hybrid CPU-MIC based architecture on the Tianhe-2 platform. Their previous work focused only on CPU-based optimization, while in this study, they leveraged both Intel Xeon CPUs and Intel Xeon Phi coprocessors (many integrated cores) MIC resources. Key optimizations include inner-outer subdomain partitioning, asynchronous data transfer, red-black relaxation parallelization, and optimized workload distribution across both CPU and MIC cores. [74] highlighted the importance of multi-coloring techniques for Gauss-Seidel with SIMD-friendly sparse matrix formats. [75] were especially concerned with improving the communication in computer systems, and their solution involved pipelined CG variants, and that kind of optimization was not allowed, as mentioned in Section 2.1.5.2. Although all these papers achieved significant improvements in performance compared to the reference implementation, they varied in their emphasis: [24] and [73] selected the use of heterogeneous structures, [70] and [74] optimized for CPU-only systems and [75] focused on communication efficiency. These works laid a solid groundwork for optimizing HPCG and other applications on the world's most powerful supercomputers, including Tianhe-2.